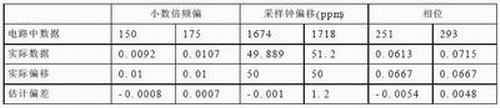

表4.1 波形图中数据与实际数据对照表

小数倍频率偏移和采样钟频率偏移模块是在整偏校完之后才有效,此时的小数倍频率偏移是经过时域粗偏估计校正后的剩余部分。表4.1列出波形中的估值与实际数据的对应关系。从表中的数字对应关系可以看出,电路中估计的小数倍频偏与实际频偏的差在0.1%以内。采样钟偏移估计值与实际偏移误差为1ppm左右,这已满足了采样钟的粗调精度;相位输出为前后符号的小数倍偏频所引起的相位旋转。由此单元电路,可以准确地估计出小数倍频偏和采样钟偏移及其相位。

细定时同步估计的电路仿真

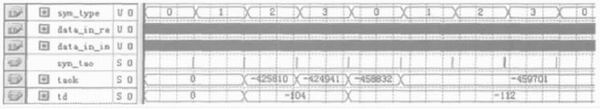

图中的data_re_in[15..0]和data_im_in[15..0]表示经公共相位校正后的复数据实虚部;syn_in是输入有用数据的起始位置脉冲;sym_type[1..0]是前端输入的符号类型;taok[22..0]和td[9..0]分别为估计的符号定时偏移和其整数部分;syn_tao是taok[22..0]的有效数据起始脉冲信号。

图4.3 符号定时偏移估计单元的电路波形图

图4.3中共有9个符号。由于本算法利用了4个符号的散布导频,故图4.3中,从第四个符号的结束处开始,在syn_tao后的taok[22..0]才是当前符号的定时偏移估计值。波形中的估值与实际数据的对应关系如表4.2所示。

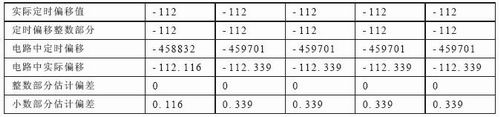

表4.2 波形图中数据与实际数据对照表

表4.2中的定时实际偏移为-112,而不是仿真条件中的-100,这是由于在瑞利信道的仿真模型中,符号定时同步头位置(重心位置)是在第一条径之后12个采样点出现的。由表中数据对应关系可知,符号定时偏移估计单元可准确地估出符号定时偏移的整数部分。由于采样钟偏移、算法估计误差及电路运算误差的影响,其小数部分不为零,这与电路的仿真结果一致。

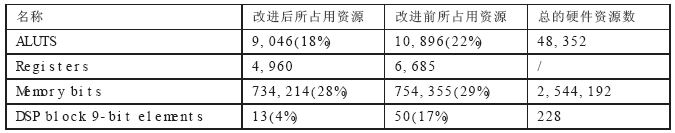

改进前后占用硬件资源比较

表4.3给出了改进前后,频域同步所占用的硬件资源比较,其中ALUTS、Registers、Memorybits、DSPblock9-bitelements分别为自适应查找表、寄存器、存储器和9字节DSP处理块。通过比较可以发现,改进后的方案可以节省大量的硬件资源。

表4.3 改进前后的硬件资源对比

结束语

频率偏移估计可以分为整数倍频偏估计单元、小数倍频偏、采样钟偏移估计单元和符号定时偏移估计单元。本文主要介绍各部分的算法方案及电路实现时所用的FPGA元件的基本结构、设计思路。最后通过对电路的仿真波形可以看出,这些频域同步算法和FPGA电路能够满足多载波传输系统的同步要求。

加好友

加好友  发短信

发短信

Post By:2010-11-12 15:28:24

Post By:2010-11-12 15:28:24