�������DAQ�豸�����Զ���ʽ���ش������ܣ�����ȵ�Ϊϵͳ��ʱ�������ṩ������ܡ� ������豸���ܵĹ̶�

ASIC��ͬ������DAQ���û���

FPGA��ϵͳ��ʱ��������������ģ�������I/O�ܹ������ض�Ӧ�ò���������Ӧ�����á� ��ָ��չʾ�ˣ����ʹ��Rϵ������DAQ�忨��NI LabVIEW

FPGA����������ִ�����ݲɼ�����

��������

����NI LabVIEW FPGAģ�����DAQϵͳ�Ŀ������������ؽ���Ӧ�ó�������ʵ�ָ�������/��������� �û�����Ԥ���˽�VHDL��Ӳ����ƹ��ߣ���ɽ�LabVIEW����Ƕ��FPGAоƬ�����Ӳ����ʱ���ٶȺͿɿ��ԡ�

�����������ȴ����ݲɼ�Ӳ���ij�������������⡣ ������ӵ����ģ��ת����(ADC)����ģת����(DAC)����������/����ߣ�������I/O��Ҫ����ʵ�ʲ�������ij�ַ�ʽ�Ķ�ʱ�Ϳ��ơ� ���͵Ķ�����ݲɼ��豸���ù�����ȫ��ASIC�������˴�����Ĺ���������

�������磺Mϵ��DAQ�豸ͨ��DAQ-STC2�������Ÿ���Ӳ������Ķ�ʱ�ʹ����� ����DAQӲ�����磺Rϵ��DAQ�豸�������������ϵ������κ����ݲɼ��豸����Ϊ�ڿ����豸���ܷ�������DAQ�û���FPGA��ϵͳ��ʱ������ȡ���˴�ͳASIC���Ӷ�ʹ������ģ�������I/O���ܸ����ض�Ӧ�ò���������Ӧ�����á� ��������FPGAоƬͨ��NI LabVIEW FPGAģ����б�̣���ʱNI LabVIEW��������ģʽ�Ծ����ã�����������һ���º���������ײ���豸I/O��

����LabVIEW FPGA I/O�ڵ㲢��ͨ��NI-DAQmx��������ʵ�ֳ�����������ܣ��������������ڸ���ͨ����ײ������С� ͨ�����¸����ֵ����ݣ����ǽ��˽�NI-DAQmx���ض�ʵ������ѧϰ���ͨ������DAQ���Ƹ������ݲɼ�����

������ʱ�ʹ���

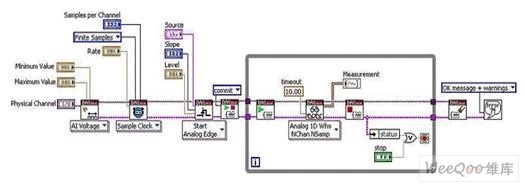

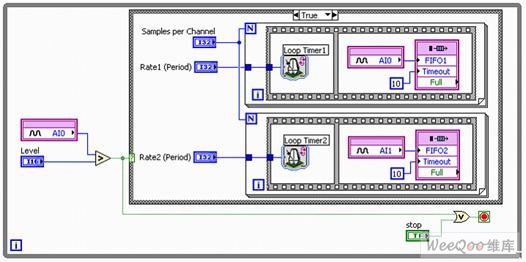

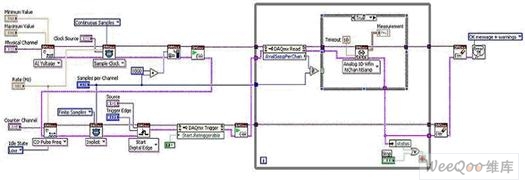

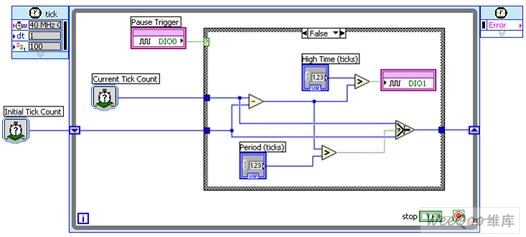

����ʵ�ָ����ݲɼ�������DAQ��Ҫ���ڶ��ƶ�ʱ�ʹ����� �·��ķ��������ͼչ���ˣ�NI-DAQmx����ʵ�ֵĴ���ʽģ����������

����ͼ1. ͨ��NI-DAQmxʵ�ֵĴ���ʽģ������

������ͼ1��ʾ������DAQ��δʹ�ò�ͬ��������ͨ��������ͨ����ΪI/O�ڵ�ĺ�����д��·ģ�������ͨ���� �����ǿ���ʹ��NI LabVIEW FPGA��I/O�ڵ�����õ���ͬ���ܡ�

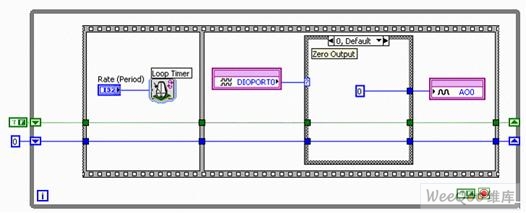

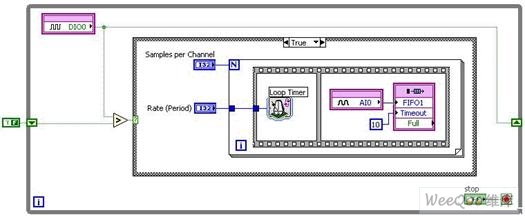

����ͼ2. ͨ������DAQ��NI LabVIEW FPGAʵ�ֵĴ���ʽģ������

������ͼ��û�����ȫ��ͨ��������ʱ�ӡ����������ú�����Ҳû�п�ʼ��ֹͣ����������� �������ݶ���1����ģ��I/O��ȡ��ȡ����ȫ����ʱ��Ϊ����LabVIEW�ṹ���磺Whileѭ���������ṹ�������ơ��������������ͼ����FPGAӲ����ִ�У�LabVIEW��������б����ֳ�Ӳ����ʱ���ٶȺͿɿ��ԡ�

���������Ǹ�������˽�һ�¸ó����ͼ�����з�ʽ�� ģ��I/O�ڵ㲢��ָ��ij���������ʣ���ʹ��Forѭ���ɼ����������� ��֮��Ӧ��ADC��I/O�ڵ㱻����ʱ������������źŽ���ʵ�����ֻ������ͨ��Forѭ�����ܶ�ʱ�� ������100 kHz��Ƶ���½����źŲ��������ѭ�����ӳپͱ����趨Ϊ10 ?s�� ѭ���Ķ�ʱ�������ӵ�2��ѭ��������ʼ��ȷ�����ض���ʱ���ӳ٣��û�����ܹ�ͨ��˳��ṹ��֤����֮�������ָ����ʱ������ NI LabVIEW FPGA*��ǿ��������ṹ��ʵ�ʴ��������ڷ�װ��������Ӳ�������� �������еĺ����ͽṹ��ͨ������Ԫ��Ӳ�������У����������ṹȷ����ʼ����ʵʱ10 ?sʱ�侫�ȵIJ����� �����ָ�����ǣ����ڲ���λ��Ӳ���㣬ֻ�漰������εij�����������û������������ID���ͷ��ڴ���

�����ͻ���FPGA������DAQӲ�����ԣ����������������ܹ����Ƹ��ඨʱ�ʹ���������Ӳ���н����źŴ����;��ߡ� �����������˽�һ�£����ij���Զ���Ӧ�ã����ģ�����봥��������Щ�ġ� ������ϣ����2·ģ������ͨ����ij·��ѹ����ָ����Χʱ�㴥���ɼ����ָ�������أ� ����NI LabVIEW FPGA�����������ִ�����練�ơ�

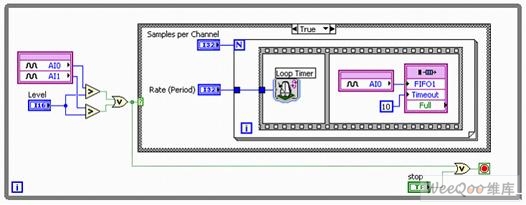

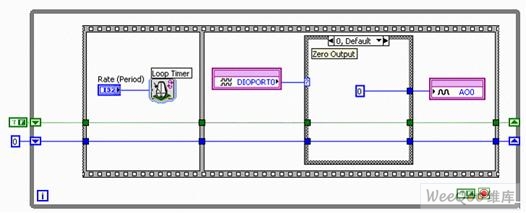

����ͼ 3. ͨ������DAQ��NI LabVIEW FPGAʵ�ֵ��Զ��崥��ʽģ������

������������Ѿ�Ϊ�����ͼ�����˵�2��I/O�ڵ�͵�2���ȽϺ������Լ�1�������������� ����DAQӲ��Ϊ���е�ģ������ͨ���ṩר��ADC�����2·ͨ���ܹ�����ͬ��������ͬʱ��ֻҪ�κ�1·ͨ���ĵ�ѹ������ָ����Χ�������ṹ���ִ�С��桱����������ʼ��10 ?sʱ�侫�Ƚ��в����� ���ס��ȱ������DAQ�㲻�����������ƵĴ�����������DAQӲ����Ӧ��ʱ��������Ҫ���и����ӳٵ�������ʱ��ʵ�֡� ����˺�����ϣ��ͨ����չ����ط�Χ��2·ͨ��������ȫ��8·ͨ��������ϣ���������ִ���������Ҫ���Զ�����롣 ����Ԥ����ɨ����û���ɶ�����ͨ�����Ͻ��в����������ݴ�����FIFO�������� ������һ�����ܶ�ȡ��FIFO�������ʹ˺�IJ�����ɾ���DMAͨ������������������

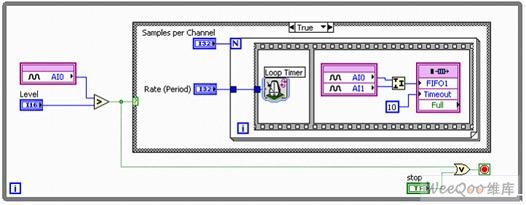

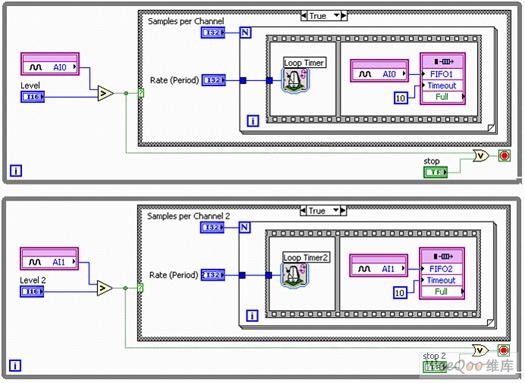

�����������ϣ������NI-DAQmx�������Ե�2ģ������ͨ�����в�������ó����ͼ��ͼ1��ʾ�������������Ȼ��������Ȼ���ڣ���Ϊ2·ͨ��������������ͬ�Ĵ�����������ͬ��ʱ��Ƶ�ʽ��в����� ��������������������DAQ��NI LabVIEW FPGA����ʵ�ֵĸ����ͨ��������

����ͼ4. ͨ������DAQʵ�ֵĴ���ʽͬ��ģ������

����ͼ4����ͼ��չ���ˣ���λ���ģ������ͨ��0�е�ģ�ⴥ��������2·��ͬ��ģ������ͨ������ͬ����������������DAQ�豸�����ж�����ADC����ͬһI/O�ڵ��е�2·ͨ��������ȫ��ͬ��ʱ�̽��ܲ����� ���͵Ķ��DAQ�豸��ͨ��һ��ADC��·��������ͨ������ˣ���·ͨ�����빲����ͬ�IJ���ʱ�Ӻʹ����ߡ� ͼ5����ͼ��չ���ˣ�����DAQӲ����ʵ�ܹ��Զ��������ʣ��Բ�ͬ��ģ������ͨ�����в����� �ڶ�����·�з���ģ������I/O�ڵ��ÿ·ͨ��������ȫ��ͬ�����ʽ��в�����Ȼ�����ͨ��2��DMAͨ����дӲ�̡�

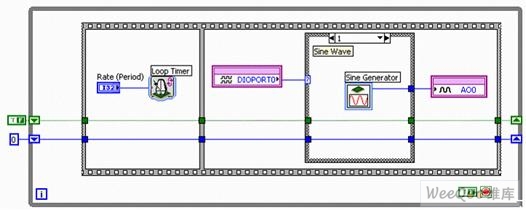

����ͼ5. ͨ������DAQʵ�ֵĴ���ʽ������ģ������

���������ָ�����ǣ���������ϣ��2·ͨ������������IJ����ʺͿ�ʼ��������ɲ���ͼ6��������I/O�ڵ㶼�����ڲ���ѭ���ṹ�С��÷�ʽ���������FPGA�IJ����ԣ�ȷ���˸��������ܹ�ʹ��ר����Դ����ִ��ʱ��ȫ�����������ɼ�����

����ͼ6. ͨ������DAQʵ�ֵĶ�������ʽ������ģ������

����ͬ��

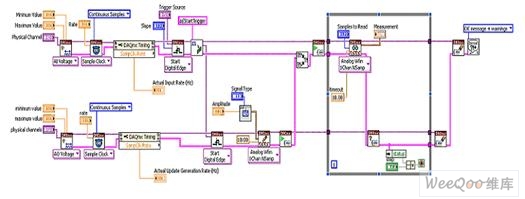

����DAQmx���������ṩ����ͬ��ѡ������������������ʱ������ԡ� ���·��ij����ͼ�У�ģ������ͨ����ģ�����ͨ���������ִ���ʵ��ͬ���������У����ģ������ָ�����ִ�������ʹ��ģ������Ĵ������źŴ�������ģ�������

����ͼ7. ͨ��NI-DAQmxʵ�ֵ�ͬ��ģ����������

�����û���ͨ������DAQӲ������ٵ�ִ��ͬ�����������������ID�Ͱ����ź�·�ɡ� ��������ʾ��NI LabVIEW FPGA�е����ݡ�

����ͼ8. ͨ������DAQʵ�ֵ�ͬ��ģ����������

�����˴��������ٴ�ͨ�������ṹ��FPGAоƬ��ִ��Ӳ��������������ͨ��0�ϵ����������������������еĴ��롣 ��˳��ṹ�У�ģ������������Ľڵ���ͬʱ���ܵ��õĹ����У�����û���κζ�����������ֻҪ���ڸ���������Whileѭ����Ƕ��ģ��I/O�ڵ㣬��������ӵ�ж����IJ������ʡ� ����ֵ��ע����ǣ� �����ͼ����ʾ������������������1��Express VI���ɰ����û��ڲ��ұ�(LUT)�н���ʽ����������ֵ��

����ͼ8�е�����DAQ�����ͼ��ͼ7�е�DAQmx VI�Ծ�����ͬ�Ĺ��ܣ���Ψ������DAQ����Ϊ�Զ��������ṩ��Ӧ������ԡ� ����Ϊ֤����������1����ͣ����������ֻ�����ڲ�Whileѭ��������1�������ṹ����ͨ����һ������I/O�ڵ�ѡ�������������������������������� ��Ӳ�����б�̵�ǿ���ܣ�ʵ���˸���I/O�Ķ�ʱ��ͬ����

�������ͬ������һ��֤����Ϊ��ͨ�����������������������岢���������������ģ������IJ���ʱ�ӡ� �ù����ǽ��п��ش���ʽ�������ij����ֶΡ� ��ͼ��ʾ�˿�չ����ɼ��������DAQmx���롣

����ͼ9. ͨ��NI-DAQmxʵ�ֵĿ��ش���ʽ����ģ������

�������ڣ������Ƕ���ͼ���ݺͳ�����ͬ���ܵ�NI LabVIEW FPGA�����ͼ�����ԱȽϡ�

����ͼ10. ͨ������DAQ��NI LabVIEW FPGAʵ�ֵĿ��ش���ʽ����ģ������

��������NI LabVIEW������Ӳ�������У�ͼ10�е��������ò�����Ȼ�õ��˼����� �����Ѿ����������������ߺ�Forѭ���ṹ��������Ӳ�����ش���ʽ���ɼ��� ͼ9�еij����ͼʹ��2�����ؼ����������������ش����������������У����͵Ķ��DAQ�豸ֻ��2���������� ������NI LabVIEW FPGA������DAQӲ��ȴ�ܹ�������һ�����������óɼ������� ���ǽ���֮��Ķ�����漰���ࡰͨ������DAQ���м�����/��ʱ���������ݡ�

���������ܹ�������Ƶ�ʴ����IJɼ�����һ�����ƽ�����DAQ��Ӳ����ʱ�������������ԡ� �û���ͨ�����ٰ��ؾ����������źŵ�Ƶ�ʣ�����ѡ�������ṹ������Ĵ��룻��һ����ʹ�õ��Ͷ��DAQ�豸�����ġ� �ڶ��豸��ͬ�������У�����DAQ�����ṩ����PCI�忨��RTSI������������PXIģ���PXI�������ߡ� ��Щ�ⲿ��ʱ��ͬ������ͨ�������ͼ�ϵ�I/O�ڵ���ܷ��ʡ�

����ģ�Ⲩ�ε�����

�������ٶ��DAQ�豸������ģ�����ͨ�����ܹ�Ϊ������������ģ�Ⲩ�ζ���Ҫ�õ�FIFO���塣 ���ɵIJ��οɽ�FIFO����ѭ����������������������������κθ������ݣ������������ϵ���������һϵ�е�ģ��ֵ�� ͨ�����ߵ����Դ�Ӱ�첻����Ϊ��û������豸��Ƶ�����ݶ�д�� �����������Ҫ�ģ��ͱ��������������������FIFOд�������ݡ� ��һ���취����Ӳ��FIFO�豸������д���ݣ������ֻᵼ������������ʱ�͡� ��������DAQ���û��ܹ��������������洢��Ӳ���������ܹ�ͨ��Ӳ�������ı䲨�Σ������������Ⲩ�η�������

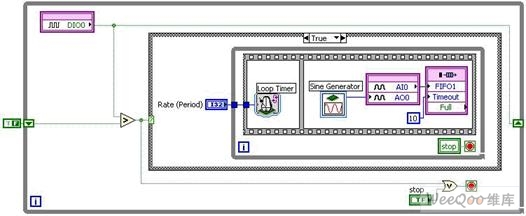

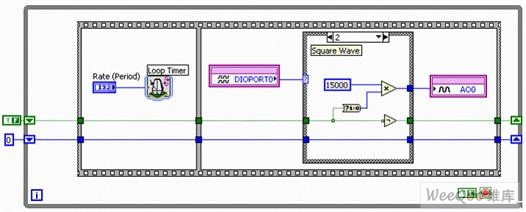

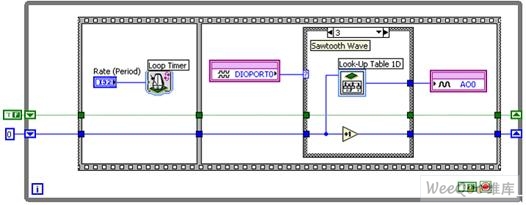

�����·��ĺ�������������ͨ�����������ߣ���������������еĸĶ��� ͨ���������I/O��0��1������ȡ����Ӧ����ģ�������4�ֲ�ͬ״̬���������

����ͼ11a. ��������DAQ����0�ĺ��������� �C �����

����ͼ11b. ��������DAQ����1�ĺ��������� �C ���Ҳ�

���������߽Գ��ֵ͵�ƽʱ��ִ������0����ͼ11a��ʾ�����ֵΪ0 V����������DIO��0���ָߵ�ƽ��DIO��1���ֵ͵�ƽʱ������1����ģ�����0��ִ�в�����һ�����Ҳ����û���ͨ�����������ɽṹ��ͼ11b���е����ҷ�����Express VI������NI LabVIEW FPGA����IJ������������������Ҳ���

����ͼ11c. ��������DAQ����2�ĺ��������� �C ����

��������2��ͼ11c���ܹ���Whileѭ����ÿ�ֵ����У������л�����ֵ�� ��ֵ�ϵ�ʱ������15000�㱻д��ģ�����AO0���Զ�Ӧ16λDAC��������Ĵ�����ŵ���ֵ��15000�� 16λ�з�������������-32768��32767֮�����ֵ���������ѹ��Χ����-10 V��10 Vʱ����ģ�����AO0д��-32768������-10 V��ѹ����д��32767������10 V��ѹ�������У������ǵ�д��ֵΪ15000�������ɵĵ�ѹ������5 V������ѧ��ʽΪ: 15000/32767 * 10 V = 4.5778 V�� ͨ��������2�����һ����0 V��4.578 V֮��任�ķ�����

����ͼ11d. ��������DAQ����3�ĺ��������� �C ��ݲ�

������DIO 0��DIO 1�����ָߵ�ƽʱ����ִ�����һ��������ͼ11d������䣬��������ұ�(LUT)��������һ����ݲ��� ��Ϊ��һ��Express VI�IJ��VI�����ܴ洢���Ⲩ��ֵ��Ҳ��ͨ����̽�������ֵ�������� �����У��������õľ�ݲ�����ģ�����ͨ��0�����ɡ�

����ͨ�������е�ֵ���洢��FPGA�ϣ��û��ڽ������������Ե�ͬʱ��Ҳȷ���˲��θ���ʱӲ����ʱ���ٶȺͿɿ��ԡ� ֮ǰ����������������ģ������Ĵ�����ͬ�������ͬ��������ģ���������������DAQ���û��ܹ��Բ�ͬ���ʣ���ȫ�����ظ��¸�·ģ�����ͨ���� ����ζ�ţ��û����ڲ�Ӱ������ͨ����������ǰ���£��ĵ��������Բ��ε�Ƶ�ʡ� ��ע�⣺��������ݲɼ�Ӳ�������߱�����ܡ�

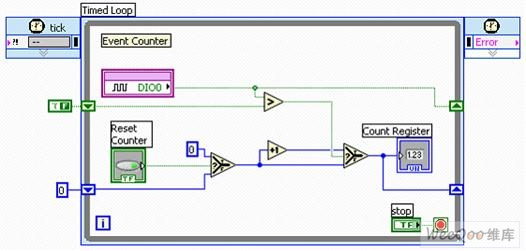

����������/��ʱ���IJ���

������ǰ���������͵Ķ��DAQ�豸ֻ��2�����ؼ�������������DAQ�����ڸ��������������м��������ܡ� ����I/O�ڵ��ܹ���NI LabVIEW FPGA��������Ϊ�����ڶ�ʱѭ����רҵ�ṹ�������û���2.5 MHz��200 MHz���ض�Ƶ�ʷ�Χ��ִ�д��롣 ���磬����40 MHz��ʱ�ӣ��û���ʹ�õ����ڶ�ʱѭ�����ڸ����������ϴ���40 MHz�������� ͼ12����ͼ��չ���˳����ͼ����ʽ��

����ͼ12. ��������DAQ�ļ��¼�������

�������ڼ���ֵ����U32��32λ���������������ͱ���������ʾ�ؼ����ô������FPGAоƬ��������1��40 MHz��32λ�������� �û��ɶ���������θ�����ճ�����ͬ�������ϵĶ�����������ܹ��˴���ȫ���е����С� ͨ��������DAQ�в��������ÿ���ʵ�ֶ�ʱ���������Զ��塣 ͨ��ѡ���û��ܹ�ÿ��2�������ر����1�μ����������������ܻ��ڼ����Ĵ�����ֵ����ģ��ɼ��� ���ิ�ӵļ������������磺���������������ɺͼ���ʽ�¼�����������Ҫʹ��2��������������ζ��ʹ�õ��Ͷ���豸�е����а��ؼ������� ���ܹ�160�������ߵİ����£�����DAQӲ���϶�ʱ����������������ܵ�I/O�����Ե�Ӱ�죬������ȡ����FPGAоƬ�Ĵ�С�� ����NI LabVIEW���������ڹ�оƬ�У�����û����衰װ����������װ����ͨ�ü�����������ȫ����Ƽ����������С�

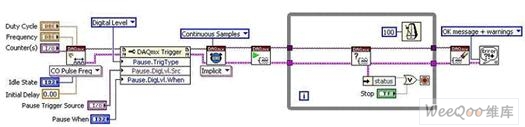

����ͼ13����ͼ���еķ���ʹ�ü�������������һ�������������в�����ͣ����������NI-DAQmx�С�

����ͼ13. �����������е����ɺ�����NI-DAQmx����ͣ������

������NI LabVIEW FPGA�У���ͣ����������������ã���Ϊֻ��������ṹ�����ڹ�оƬ��ʵ����ͬ�Ĺ��ܡ� �˴���ͨ������DAQ����ʱ��չ�ֵ���ͬ���ܣ�ͼ14����

����ͼ14. �����������е����ɺ���������DAQ����ͣ������

��������������£�����I/O��DIO0������ͣ�����������彫������I/O��DIO1�����ɲ������ʹ�õ����ڶ�ʱѭ���������������25 ns�ķֱ��ʣ���Ϊ�⽫��Ϊ������ʱ��ʹ��40 MHz��ʱԴʱ��ֵ��

��������I/OӦ��

��������DAQӲ���ṩ���160��Ӳ����ʱ�����ߣ����������Ӧ�ó�Ϊ���ܡ� �����Ѿ�ѧϰ�����ʹ������I/Oʵ�ִ�����ͬ����������/��ʱ�������У�������DAQ�������������ʲ��ԡ�����ģʽƥ�䡢������ȵ��ơ�����������������ͨ��Э�顣 �Զ�������ʽ�Ĵ��нӿھ���ֱ��ͨ�����ֶ�ʱ��ͼ�����ʵ�֡� ����˵����SPI����һ����Ӳ��������磺��������ADC������ͨ��ʱ��õ�����Э�顣 ͼ15����ͼ��չ�����ڽ���16λSPIͨ��ʱ��3����Ҫ����������Ӧ�Ķ�ʱ��ͼ��

����ͼ15. SPIͨ�����붨ʱ��ͼ

�����綨ʱ��ͼ��ʾ������16λ���ݾ���ÿ��ʱ��������˳�δ��ݣ���Ƭѡ�����ߣ�chip select line)����ֵ͵�ƽ�� ���ڣ�������������NI LabVIEW FPGA�У����ͨ������DAQӲ���ϵ�3�������߽��д����̡�

�Ӻ���

�Ӻ���  ������

������

Post By��2010-11-20 9:25:13

Post By��2010-11-20 9:25:13

�Ӻ���

�Ӻ���  ������

������

Post By��2010-12-4 21:36:53

Post By��2010-12-4 21:36:53