显然,FPGA在并行化与流水化方面存在相当大的优势,同时与GPGPU相比,FPGA在主缓存与带宽方面也存在优势。在FPGA中,逻辑资源周围是存储器块。XDI模块具有一块带宽为3.8TB/s的3.3MB主缓存,这是nVidia 8800 GTX型GPGPU上主缓存(支持流处理器)的5~10倍。

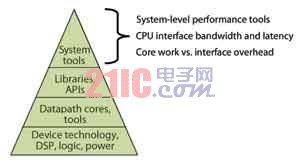

FPGA的优势还在于,可以利用裕量连接带宽来灵活构建直达各逻辑块的数据通道和存储器访问通路。图1所示的可编程互连结构提供了大量的布线带宽。模块与电路板可根据FPGA输出带宽、存储器大小及延迟的需要进行设计,I/O端口可由用户自定义。

图1 FPGA的架构

最后,FPGA架构还拥有一个优势,它可扩展为更大型的逻辑块、存储器块与DSP块的阵列。逻辑与主缓存的大小是一起扩展的。现有最大的FPGA峰值功耗为30W,其FPGA架构有很多空间,可以在不超过现有数据中心功率和冷却限制的前提下,扩展为新的处理构型。

尽管FPGA架构具有许多出众的性能,一些性能必须共同发挥作用,才能提供优于CPU协处理的解决方案。

芯片与算法基础

大部分双精度浮点算法的加法与乘法操作比例大约为1:1。在FPGA中,加法运算使用逻辑资源,乘法运算使用DSP块,因此FPGA的逻辑资源与DSP块的比例必须均衡。FPGA的另一个特点是其可编程功率技术,该技术可针对所有逻辑块、DSP块与存储器块进行编程,根据设计的时序要求将其设定为高功耗或低功耗模式。

浮点运算核已经改进,可运行于更高的时钟速率,使用更少的DSP块和更少的逻辑资源。采用浮点编译器可减少不同浮点运算核之间用于连接64位数据通路的逻辑资源。

在一次浮点运算结束时,合并对浮点运算进行规格化处理(定点格式转换至浮点格式)的步骤,可以显著减少对后续浮点运算输入的去规格化处理(浮点格式转换为定点格式)。浮点运算的数学表达式的整个数据通路可熔接在一起,这会最多减少40%的逻辑资源并使时钟速率略有提高。

浮点运算的正确组合十分重要。如果算法有许多超越运算(求指数、求对数等),FPGA可配置所需要的数目。在GPGPU设计中,会增加一些硬模块实现上述函数,但比例比单精度浮点逻辑少得多。使用算法技巧、抽象硬件细节及针对个别FPGA资源的优化都需要函数库。

基于芯片、算法与库基础,图2的系统级解决方案涉及到了工具链、模块/板级设计、CPU接口以及采用合作公司专门技术的由CPU至基于FPGA的加速器的数据传输。

图2 FPGA加速系统级解决方案的基础

[此贴子已经被作者于2010-11-17 11:59:14编辑过]

加好友

加好友  发短信

发短信

Post By:2010-11-12 14:31:37

Post By:2010-11-12 14:31:37