0 引 言

当前普遍使用的DSP语音处理技术只能对语音进行简单处理,不能适应语音业务的多样化趋势。本文介绍利用MPC860和VxWorks实现综合语音通信平台,支持多板卡、多路语音实时传输,可扩展多路语音共听功能。利用MPC860的通信和信号处理功能,且Vx-Works具有占用空间小、执行效率高、方便进行个性化定制和较好的兼容性等特点,所以该综合语音通信平台在功能、硬件结构、体积、功耗以及灵活性上具有较大优势。

在设计中尽量采用嵌入式开发中的常用器件,以便稍加改动即可应用于其他设计。可以根据实际需要更改系统中语音通道的数目和扩展多路语音共听功能等。

1 系统结构及工作原理

1.1 系统组成及特点

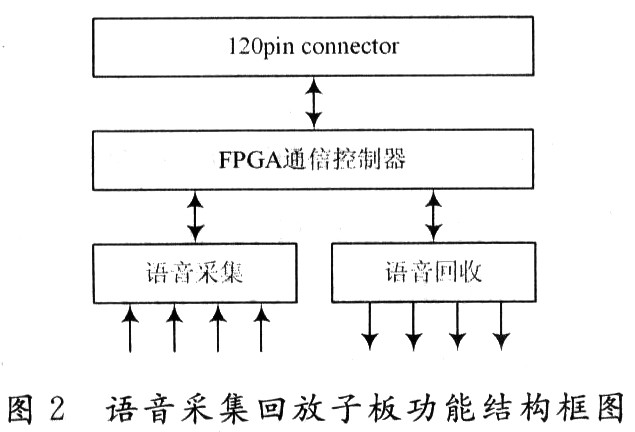

整个通信平台由语音通信处理主板和语音采集回放子板组成。语音通信处理主板包括CPU MPC860、FLASH存储器、SDRAM存储器、10/100Mb/s网络接口、RS 232串口、BDM调试接口、Console接口、供电和复位电路及120pin连接器。通信处理主板的核心MPC860是Motorola公司的一款由MC68360演变而来的通用单片集成嵌入式微处理器,适用于通信和网络系统。该微处理器内部有两个处理器:PowerPC和32位RISC处理器。PowerPC核同内存管理单元(MMU)、指令和数据Cache一同处理高层次应用,CPM则负责完成低层数据通信。两个处理器主要通过共享内存交互。通信处理模块利用SCC,SMC,SPI和I2C串行通道与外部设备通信,其中SCC和SMC支持时分复用。设计中,SCC工作在QMC协议Trans-parent Mode。通信处理模块(CPM)新增了数字信号处理(DSP)功能。语音采集回放子板由语音采集电路、语音回放电路、基于FPGA实现的通信控制器和与语音通信处理主板连接的120pin连接器组成。

由于MPC860的数据传输速度相比ADC和DAC要快很多,设计相应的逻辑电路控制语音的采集和回放、协调MPC860和数据采集、回放电路之间的通信是保证系统正常工作的关键。文中设计了基于Altera公司的CycloneⅡEP2C8芯片实现的通信控制器来解决这一问题。

将通信平台分为语音通信处理主板和语音采集回放子板分别设计实现,是为了降低系统开发难度和便于系统维护、升级和扩展。例如语音通信处理主板无需改动即可利用已有的连接器、FEC网络接口和SDRAM存储器等资源与视频编解码芯片、视频压缩/解压缩芯片组成网络视频服务器。

1.2 功能结构和工作原理

语音通信处理主板的功能结构如图1所示。

系统上电后,语音通信处理主板复位电路产生复位信号,MPC860接收到复位信号后,跳转到0X100处开始执行启动代码。按照BSP配置逐步执行CPU初始化、板上其他硬件电路的初始化、操作系统运行所需数据结构的初始化、启动VxWorks WIND内核、创建UserRoot任务、初始化系统中用到的可选扩展模块(如I/O系统、文件系统、网络协议等)、创建任务usrAppInit(),此时语音通信平台准备就绪,可以执行语音通信任务。采集板的功能结构如图2所示,语音通信处理主板启动完毕后,语音采集回放子板可在通信控制器控制下采集和回放语音,并对语音数据进行压缩编解码和IP封装、解封装处理。

1.3 数据处理流程

MPC860T和ADC AD7825,DAC AD7305之间的通信由通信控制器控制。通信控制器由数据缓冲区(Rx FIFO,Tx FIFO),基于FSM(有限状态机)实现的控制逻辑(Rx control,Tx control)和8位串并、并串转换器,时钟电路组成。其数据接收过程为:接收控制逻辑(Rx control)控制ADC AD7825将各个通道的语音数字化,并把转换结果存入接收缓冲区(Rx FIFO),直至Rx FIFO满时Rx control开始向MPC860T提供周期性帧同步信号,频率为32 kHz。MPC860在帧同步信号和时钟信号的驱动下读取Rx FIFO中的数据到SCC数据接收缓冲区。Rx FIFO读空(即读指针追上了写指针)后,Rx control停止向MPC860发送帧同步信号终止数据传输,同时向MPC860发送中断信号IRQ3,MPC860响应中断把数据从接收缓冲区读到接收ring buffer中等待应用程序处理。其数据发送过程为:MPC860完成IP解封装、解压缩后的语音数据将会在检测到发送缓冲区可用时,输出到SCC发送缓冲区,通信控制器提供发送帧同步信号驱动数据传输到Tx FIFO(发送缓冲区),待到Tx FIFO满时停止发送帧同步信号。数据发送完后,CPM会清零,TxBD)中的R位表示MPC860可向SCC发送缓冲区中装入新的数据,为下次传输做准备。

1.4 QMC通信协议

多通道控制器(QUICC Multichannel Controler,QMC)是为了实现时分复用数据传输而设计的,它可以把时分复用帧的数据分发到多达64个逻辑通道。该模式下把每一帧的数据划分成若干个时隙(Timeslots),每时隙8 b。在时隙分配表中规定每时隙数据从属于某个通道,每个通道都有一组特定的缓冲区描述符和相应的缓冲区。一个时隙的数据在收发时被放置在特定的缓冲区里,MPC860T就可把分散的数据聚集在一起发送,或把聚集在一起的数据分发到各自专用的缓冲区,而不需要额外的处理来区分各种各样的数据流。

2 BSP 设计实现

设计中软件开发主要包括启动代码的编写、操作系统的移植、硬件驱动程序和语音编、解码和IP封装、解封装应用程序。篇幅有限,本文仅介绍BSP移植。BSP即板级支持包,其功能为硬件、软件初始化、工程影像的下载和设备驱动等。

2.1 BSP的定制

无论是BootRom还是VxWorks都要使用BSP代码,BSP定制需要根据硬板配置、系统设计需求、软件功能等实际情况。实际开发过程中,为了缩短产品开发周期,通常以WINDRIVER公司的BSP模板或者第三方公司提供的可供参考的BSP为基础,根据软硬件具体配置进行修改,添加新的程序驱动新增硬件和功能。本课题中先把APC860开发板的BSPMPC860TEVB拷贝到installdir:\Tornado\target\collfig\ppcs860目录下,主要做下列修改。

2.1.1 config.h文件

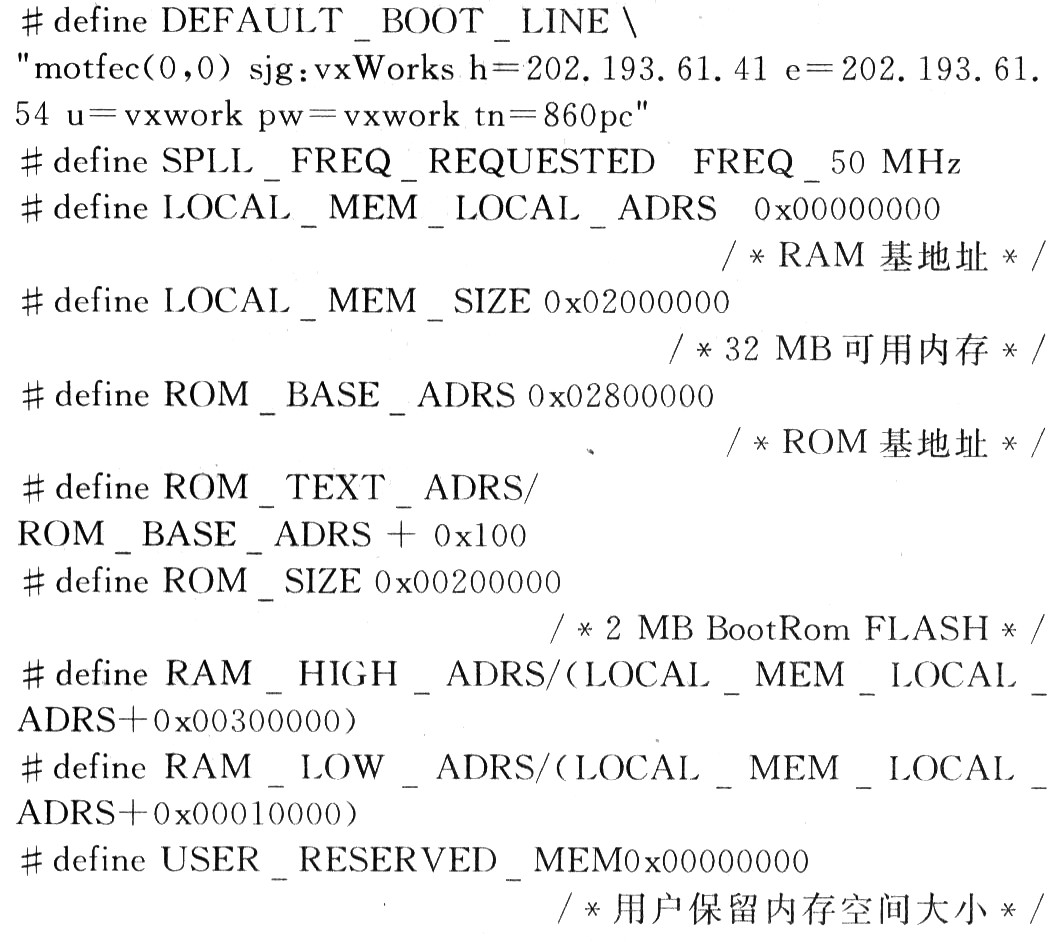

根据实际情况,需要修改启动行,内存地址、容量等配置,修改部分代码如下:

2.1.2 makefile文件的修改

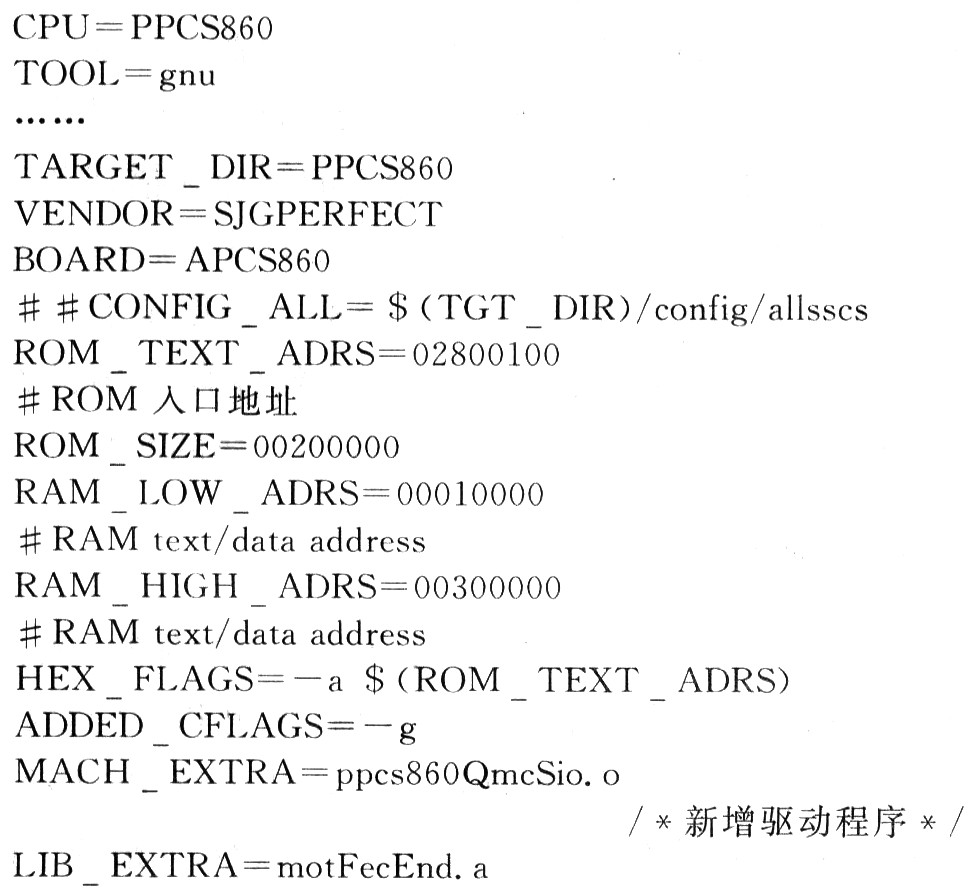

makefile文件的修改,部分程序如下:

加好友

加好友  发短信

发短信

Post By:2010-12-1 9:22:15

Post By:2010-12-1 9:22:15