CADENCE PCB设计

解决方案能为解决与实现高难度的与制造密切相关的设计提供完整的设计环境,该设计解决方案集成了从设计构想至最终产品所需要的一切设计流程,包含设计输入元件库

工具、PCB编辑器和一个自动/交互连布线器,以及用于制造和机械CAD的

接口,并且随着设计难度和复杂性的增加,可通过统一的数据库架构,使用模型和库为Cadence OrCAD和

Allegro产品线提供完全可升级的PCB解决方案,加速你的设计速度并扩大设计规模,从而提高了设计效率,缩短了设计周期,以及更快地实现量产。

Cadence PCB设计解决方案集成在以下产品中:

Cadence Allegro PCB Design LXL和GXL

Cadence OrCAD PCB Designer、Cadence OrCAD PCB Designer with PSpice以及Cadence OrCAD PCB Designer Basics

Cadence OrCAD EE Designer 和 Cadence OrCAD EE Designer Plus

优点

可靠、可升级、可节约成本的PCB编辑和布线解决方案,并随设计的需求而时刻更新

提供从基础/高级布局和布线到战略性规划和全局布线的完整的互联环境

使用高速规则/约束加快高级设计

包含一套全面的功能组合

包含一个从前端到后端的约束管理系统,用于约束创建、管理和确认

通过应用软件的整合提高设计效率

可实现前端到后端的紧密结合

功能特性

PCB编辑器技术

PCB编辑环境

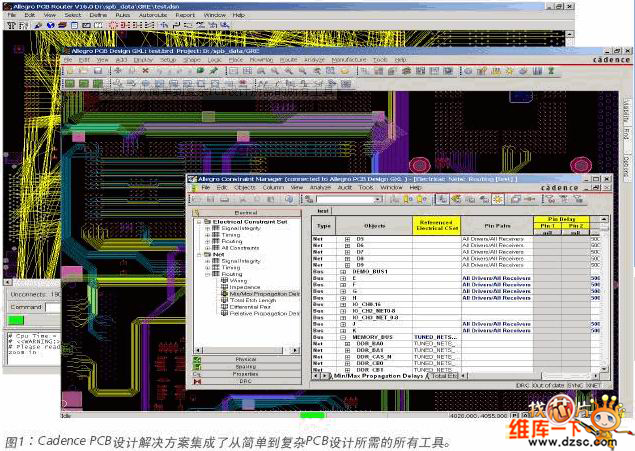

Cadence PCB设计解决方案的核心是PCB编辑器,这是一种直观的、易于使用的、约束导向型的环境,方便用户创建和编辑从简单到复杂的PCB。它广泛的功能组合解决了当今设计和制造中存在的各种问题。该PCB编辑器提供了强大而灵活的布局规划工具,基于Allegro平台的PCB设计分割技术提供了同步设计功能,其功能可缩短布线时间,并加速产品更早的上市,强大的基于形状的走线推挤功能带来了高生产效率的互联环境,同时可实时地显示长度和时序容限,动态铺铜功能提供了在放置和布线迭代时的实时铺地填充和修复功能,该PCB编辑器还可以产生全套底片加工,裸板装配和测试输出,包括Gerber 274x、NC drill和各种格式的裸板测试,见图1。

约束管理

约束管理系统实时地显示了物理/间距和高速规则以及它们的状态,根据设计当前所处的状态,并且可适用于设计过程的任一阶段,每个工作表提供了一个电子数据表界面,能够让用户以层级的方式进行定义,管理和确认不同的规则。这种强大的功能应用可以让设计师用图形创建、编辑和评估约束集,使其作为图形的拓扑结构,当作理想的实现策略的电子蓝图。一旦约束被提交到数据库中,它们就可被用来驱动信号线的放置和布线过程。该约束管理系统是完全集成到PCB编辑器中,而约束可以随着设计过程的进行而被实时地确认,确认过程的结果是用图形化的方式表示约束条件是否满足。满足约束用绿色显示,不满足约束就用红色显示,这可使设计师可以及时地看到设计的进度,以及因电子数据表中任何设计变动而产生的影响。

布图规划与布局

约束和规则驱动的方法有利于强大而灵活的布局功能,包括互动和自动的元件布局,工程师或设计师可以在设计输入或布图规划阶段将元件或支电路分配到特定的区域,可以通过REF、封装方式、相关信号名、零件号码或原理图表/页面号码来过滤或选择元件。当今的电路板上有成千上万种元器件,需要精确的管理,通过实时的器件装配分析和反馈,得以实现器件装配时从整体上来考虑并满足EMS规则,以提高设计师的设计速度和效率。DFA(可装配型设计)分析。Allegro PCB Design XL和GXL有提供实现了在互动式元件放置时,实时地进行DFA规则检查,基于一个器件类型和封装排列的二维电子表格,DFA可以实时地检查器件的边到边,边到端或端到端的距离是否违反最小要求,使得PCB设计师可以同步地放置元器件以实现最优的可布线性,可生产性和信号时序要求。

加好友

加好友  发短信

发短信

Post By:2010-12-8 14:03:13

Post By:2010-12-8 14:03:13